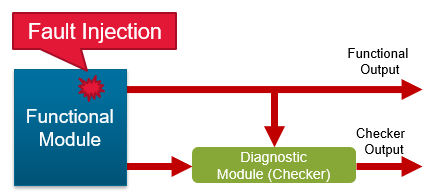

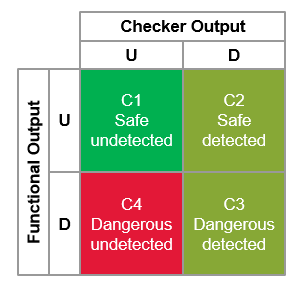

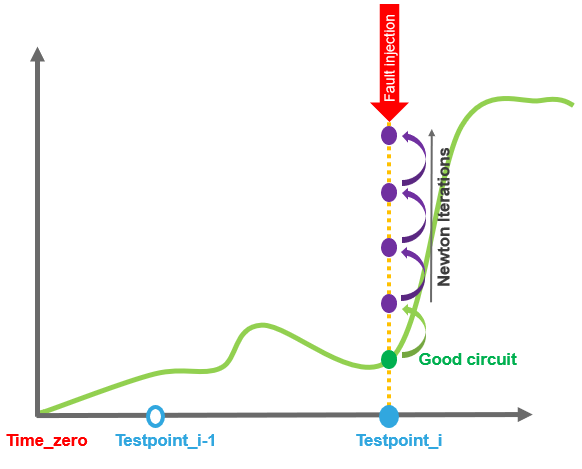

In the AMS flex mode, you can perform the analog fault analysis of the Legato Reliability Solution. The fault analysis provides a transistor-level simulation capability that can be enabled in an analog test methodology to improve test coverage by identifying critical test patterns. The following figure depicts how fault simulation functions.

Example:

|

Fault Simulation Use Model

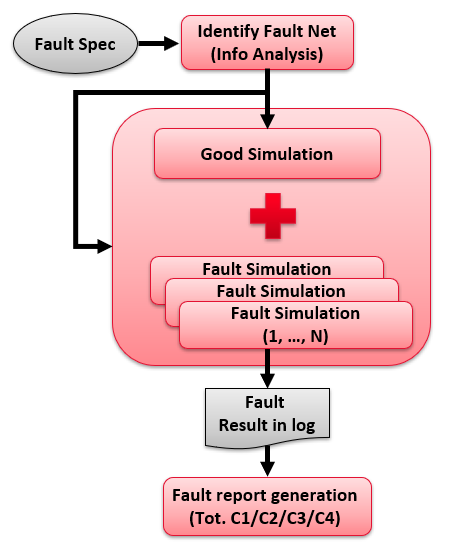

The following figure depicts the use-model of the fault simulation.

Fault analysis is done in the following steps:

Identifying the fault injection nets - fault injections are applied to device or nets.

Performing good and fault simulation - sweep one good and multiple fault simulations.

Analyzing the simulation results - generation of fault reports.

You can perform the fault analysis in AMS flex mode using one of the following approaches:

Direct Fault analysis: In the direct fault analysis flow, faults are injected at the beginning of each analysis type, such as dc, ac, transient, and so on. This mode provides the most accurate results. However, when the number of faults is large, the simulation takes much longer to complete.

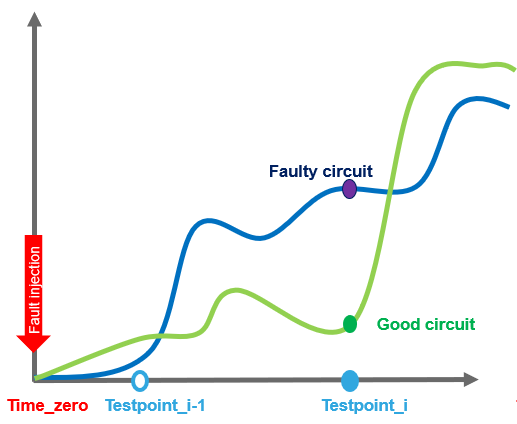

Transient Fault Analysis: To address the challenge of long simulation time, a new algorithm has been implemented in transient fault analysis. In this simulation flow, a circuit with fault list is simulated together with the fault times specified on the time axis. Spectre starts regular transient analysis till the time reaches the fault time point. Then, at each fault time, following actions are performed:

- Fault-free transient state is saved

A fault is injected into the circuit

With fault-free state used as the initial condition, transient fault simulation is continued with regular time step control and accuracy settings

The result is saved and the database is cleaned when all fault solutions are found

Fault-free transient simulation is restored and continues till the next test time point

AMS Designer Spectre Fault Analysis Integration

AMS Designer supports checkers from the digital domain using the $cds_violation system function. You can write your own checker modules in Verilog-AMS or SystemVerilog with this system function embedded.

$cds_violation ("assertName", "assertMessage", assertType);

Here, assertType can be 0: None; 1: func, or 2: check ). Type 1 and 2 are both for fault-related asserts that will be covered for the functional safety report generation.

AMS Designer supports Spectre functional safety report generation executable file spectre_fsrpt. Following is the use model:

%…/bin/spectre_fsrpt xrun.log -o report_file.txt

Note that the program must be executed under the simulation directory.