In VHDL, you use a colon to separate path elements. A full path begins with a colon, which represents the top-level design unit. The first path element is an item in the top-level scope. The following are examples of fully specified paths:

:vending

:vending:drinks

:vending:drinks:sig2

Relative paths do not begin with a colon. For example, if the current debug scope is :vending, the path drinks refers to a scope within the scope vending , which is within the top-level design unit.

In a mixed-language simulation, you can use a period or a colon as the path element separator. The Spectre AMS Designer Simulator uses the following rules:

- If the path begins with a colon, the path is a full path starting at the VHDL top-level scope. A colon by itself refers to this scope. You cannot use any other special character at the start of a path.

- If the path does not start with a colon, and the first path element is in the current debug scope, the path is relative to the debug scope. If the first path element is not in the current debug scope, the simulator assumes that the path is a full path whose first path element is the name of one of the top-level Verilog-AMS modules.

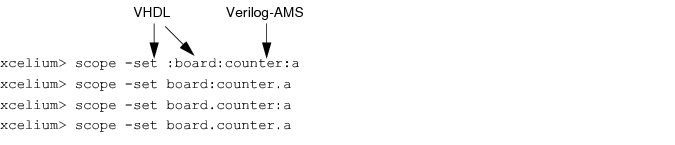

For example, suppose that you have a mixed Verilog-AMS and VHDL design, where the top-level design unit is VHDL. With Tcl commands, you can use both path element separators interchangeably (except at the beginning of a path, as specified above), as shown in the following examples:

Because VHDL is case insensitive (except for escaped names) and Verilog-AMS is case sensitive, each element of a mixed language path is either case sensitive or case insensitive, depending on its language context. When the parser looks for a name in a Verilog-AMS scope, it is case sensitive; when it looks for a name in a VHDL scope, it is case insensitive.

The syntax that you use for name expressions is also interchangeable. Name expressions are bit-selects, part-selects, and array element specifiers in Verilog-AMS, and array element and record field specifiers in VHDL. Index specifiers are also used in VHDL scope names when the scope is created by a for-generate statement.

Verilog-AMS index specifiers use square brackets, and a colon separates the left and right bounds of the range (for example [7:0]). VHDL index specifiers use parentheses, and the keyword TO or DOWNTO separates the left and right bounds of the range (for example, (7 downto 0)).

You can use either style with VHDL index ranges. Using a colon in a VHDL index range is the same as using the direction with which that index range was declared.

Record field specifiers apply only to VHDL objects. Use a period to separate the object name from the record field.

The following pairs of Tcl commands are identical.

xcelium> scope foo_array(2)xcelium> scope foo_array[2]

xcelium> value sig[7:0]xcelium> value sig(7:0)

xcelium> value sig[7]xcelium> value sig(7)

xcelium> describe sig[7 downto 0]xcelium> describe "sig(7 downto 0)"

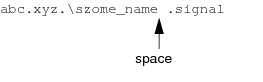

You can use either Verilog-AMS or VHDL escaped name syntax in paths. For Verilog-AMS, escaped names begin with a backslash and are terminated with a space. For example:

For VHDL, escaped names begin and end with a backslash (for example, \w3.OUT\ ).

The following two value commands are identical:

xcelium> value top.vending.@{\w3.OUT }

xcelium> value top.vending.@{\w3.OUT\}