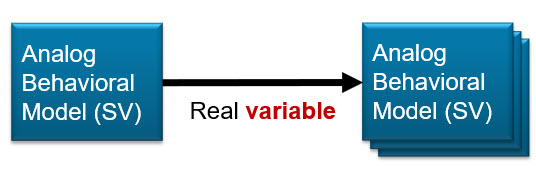

In SystemVerilog-2009, there is no concept of real-valued nets. To provide a similar capability as real signals, real data types are can be defined as variables to be driven like nets. That is, real variable port connections can be passed between modules by copying values between variables.

You can drive a real variable with a continuous assign:

real r, xr;assign r = xr;

Here, the variable r is updated whenever the value of xr changes.

Since non-collapsed ports are modeled as continuous assigns, a salutary effect of this is the ability to connect variables as a “reader” to port, either:

- Connected to an output port, or

- Declared as an input port

Here, SV real ports must be declared as:

input real p,n;output real out;

Example

The following is an example of a simple amplifier with real variable input/output

module realAmp (p, n, out); input real p,n; // real variable inputs output real out; // real variable outputs parameter real Av=50; // gain from input to output [V/V] parameter real Vhi=2.5,Vlo=0; // output voltage limits [V] real Vnom; // local variable: nominal output

always_comb begin // evaluate when any variable changes Vnom = Av*(p-n); // compute nominal output if (Vnom>Vhi) out = Vhi; // saturated high else if (Vnom<Vlo) out = Vlo; // saturated low else out = Vnom; // normal output endendmodule

Limitations

However, there are certain limitations with real variables in SystemVerilog and Verilog:

- No support for inout ports. Supports only input and output direction ports

- Real value resolution functions for multiple-driver nets are not supported. It actually forbids multiple drivers for variable ports

- No support for X/Z state

- Limited connectivity to analog models

- No Discipline association