SystemC is a digital-only language. For that reason, the Xcelium simulator with mixed-signal option uses Verilog-AMS wrappers with purely digital ports and SystemC shells to instantiate Verilog-AMS and VHDL-AMS modules within SystemC. Verilog-AMS wrappers are required only if the Verilog-AMS and VHDL-AMS modules contain a mix of analog and digital ports. Instantiations of Verilog-AMS and VHDL-AMS modules (which have purely digital ports already) do not require wrappers and use only SystemC shells. To translate analog signals to and from the digital signals of the SystemC language, Xcelium simulator with mixed-signal option uses connect modules and interface modules.

When using SystemC models with the Xcelium simulator with mixed-signal option, the following restrictions apply:

- You must not instantiate a Verilog-AMS module that instantiates a VHDL-AMS module

- You must not instantiate a VHDL-AMS module that instantiates a Verilog-AMS module

See the following topics for more information:

Preparing and Using Wrappers and Shells

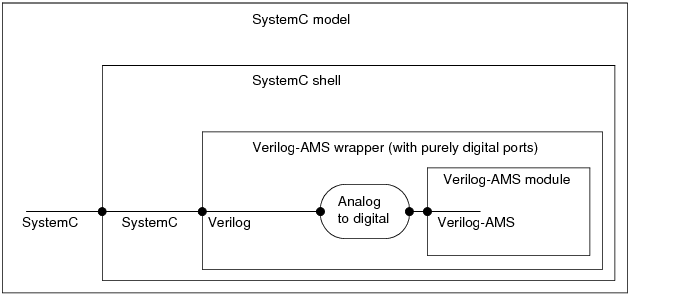

As the following diagram illustrates, the Xcelium simulator with mixed-signal option uses both a Verilog-AMS wrapper with purely digital ports and a SystemC shell for Verilog-AMS modules that are instantiated in SystemC models. The Verilog-AMS wrapper has only digital ports, so analog signals in the Verilog-AMS module instantiated within it must be converted to digital signals by connect or interface modules. The connect or interface modules are instantiated in the Verilog-AMS wrapper. The SystemC shell provides the mechanism for instantiating the Verilog-AMS wrapper in the SystemC model.

The hierarchy of shells and wrappers for instantiating a VHDL-AMS module (not illustrated here) parallels that for Verilog-AMS.

You can create the Verilog-AMS wrapper and the SystemC shell using the xmshell command.

The wrapper generated by the xmshell command is an ordinary Verilog-AMS module (but with purely digital ports), which appears in scopes and in hierarchical names. Except when the port of the imported module is analog, each port of the wrapper has the same direction as the corresponding port of the imported Verilog-AMS or VHDL-AMS module. When the port of the imported module is analog, the port of the wrapper always has the direction inout. This practice has the advantage of better supporting driver-receiver segregation, but the disadvantage of allowing only bidirectional connect modules to connect to the port of the wrapper.

Preparing Interface Modules

Interface modules are custom-designed modules used to establish the digital-to-analog and analog-to-digital data communication required to connect Verilog-AMS or VHDL-AMS ports to SystemC nets. Interface modules have these characteristics:

- Each interface module can be declared either as a

moduleor aconnectmodule. The latter declaration creates a true connect module capable of driver-receiver segregation. The former creates a more flexible module, but one that is incapable of driver-receiver segregation.

- Interface modules must have two ports, one declared as analog and the other as non-analog. The analog port can have any kind of scalar or vector discipline. The non-analog port can have any kind of discrete discipline.

- Interface modules can use any kind of analog to non-analog and non-analog to analog conversion logic.

If a connect module provides the characteristics you need, you can take advantage of the support that connect modules supply for driver-receiver segregation. Like interface modules, you specify connect modules on the xmshell command using the -analogim option.

You can only use connect modules, however, if the port of the imported module and the net of the SystemC model are compatible. The compatible port and net values are listed in the same row of the following table.

|

SystemC Net |

Description |

VerilogEquivalent |

Verilog-AMS, VHDL-AMS port |

|---|---|---|---|

|

bool, sc_bit |

2-state Boolean |

logic wire |

scalar analog |

|

sc_logic |

4-state logic |

logic wire |

scalar analog |

|

sc_bv<W> |

vector of 2-state |

logic [W-1 : 0] |

analog [W-1 : 0] |

|

sc_lv<W> |

vector of 4-state logic |

logic [W-1 : 0] |

analog [W-1 : 0] |

|

sc_int<W> |

<W> bit signed integer |

logic [W-1 : 0] |

analog [W-1 : 0] |

|

sc_uint<W> |

<W> bit unsigned integer |

logic [W-1 : 0] |

analog [W-1 : 0] |

|

char |

character/8-bit signed int |

logic [7:0] |

analog [7 : 0] |

|

unsigned char |

character/8-bit unsignedint |

logic [7:0] |

analog [7:0] |

|

short |

16-bit signed integer |

logic [15:0] |

analog [15:0] |

|

unsigned short |

16-bit unsigned integer |

logic [15:0] |

analog [15:0] |

|

sc_fixed<W,I,Q,O,N> |

templated signed fixedpoint |

logic [W-1 : 0] |

analog [W-1 : 0] |

|

sc_unfixed<W,I,Q,O,N> |

templated unsignedfixed point |

logic [W-1 : 0] |

analog [W-1 : 0] |

|

int , long |

32 bit integer |

logic [31:0] |

analog [31:0] |

|

unsigned int, unsigned long |

32-bit unsigned integer |

logic [31:0] |

analog [31:0] |

|

long long |

64-bit signed integer |

logic [63:0] |

analog [63:0] |

|

unsigned long long |

64-bit unsigned integer |

logic [63:0] |

analog [63:0] |

|

double |

real data type |

logic [63:0] |

analog [63:0] |

|

float |

real data type |

logic [63:0] |

analog [63:0] |

If you need to connect combinations other than those in the table, an interface module gives you more flexibility.

Example: Interface Module for Connecting SystemC Double to Verilog-AMS Electrical

This example assumes that you need to instantiate a Verilog-AMS module in a SystemC model and that the electrical port of the Verilog-AMS module is to be connected to a real double signal in the SystemC model. The lack of support for wreal and 64-bit logic wires in connect modules means that this example requires an interface module.

The following interface module is one possible solution. This module converts a 64-bit vector logic signal (lv) into an electrical signal (ev).

`include "discipline.vams"

`include "constants.vams"

module LV2EV_64 (lv, ev);

inout [63:0] lv;

logic [63:0] lv;

inout ev;

electrical ev;

real r;

always @(lv)

begin

r = $bitstoreal (lv);

end

analog

begin

V (ev) <+ transition (r, 1n, 1n, 1n);

end

endmodule

To use this interface module, you use an xmshell command such as the following

xmshell -ams -mess -import verilog -into systemc -sctype p1:double

-analogim p1:work.LV2EV_64 lib.vlogams_child

This command creates a Verilog-AMS wrapper with purely digital ports called vlogams_child_NCSCAMS and a SystemC shell called vlogams_child_NCSCAMS, and uses these to connect the electrical port and the double signal.

Guidelines for Using AMS Modules in SystemC Models

The following guidelines apply when using SystemC models:

- SystemC models do not fully support automatically-inserted connect modules. The elaborator does not support using an automatically-inserted connect module when used between a Verilog-AMS or VHDL-AMS module and a digital net that runs all the way through the hierarchy into the SystemC level. The elaborator does support manually inserted connect modules in this situation, but then driver-receiver segregation does not occur and the connect modules are handled as ordinary modules. If the digital net does not reach into the SystemC level, both manually and automatically inserted connect modules are fully supported.

- SystemC models do not support values in imported Verilog or Verilog-AMS modules. The

xmshellprogram does not allow you to import Verilog or Verilog-AMS modules that usewrealports. This limitation precludes connecting SystemC double values with Verilog or Verilog-AMS electrical orwrealvalues.

- SystemC models do not support passing parameters to interface modules. No means is provided in the

xmshellprogram to pass parameters to interface modules.

- SystemC models offer limited compatibility checking. The

xmshellprogram performs only limited checking on the compatibility of interface module ports and imported module ports. Thexmshellprogram does not check data type or discipline compatibility.

- Discipline resolution results are not available to the

xmshellprogram. Ports declared aawirein imported modules can resolve to either continuous or discrete after discipline resolution. Thexmshellprogram, however, is used prior to discipline resolution and so the ultimate discipline of ports declared aswireis unknown. Thexmshellprogram assumes that a wire is non-analog and connects the non-analog port of the interface module to it. This choice might, or might not, be correct.