Introducing the Common Power Format

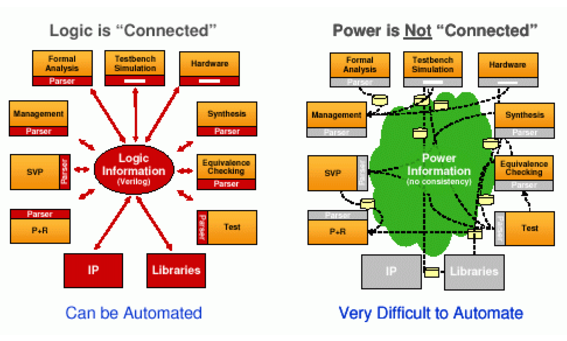

The shift in the use of chips to consumer applications and the change in the latest process technologies have made power one of the primary design criteria for a majority of the chips worldwide. However, the industry's design infrastructure has not evolved at the same pace. Figure1-1 shows the mature state of the infrastructure for functional designs versus the chaotic state of the infrastructure for designs using advanced low power design techniques.

Figure 1-1 Comparison of State of Infrastructures for Functional Designs and Advanced Low Power Designs

To accomplish an industry-wide solution for this industry-wide problem, every effort was made to use an open and inclusive approach to create a complete and well architected solution.

The lack of support in the infrastructure for designs using advanced low power design techniques has resulted in a gap between the design techniques needed to control power dissipation and the ability of the design environment to support those techniques in a safe and efficient manner. The Common Power Format has been architected to supply the infrastructure needed to support the state of the art in low power design styles and techniques.

The requirements for the Common Power Format were created using a wide range of viewpoints and with a broad range of applications in mind:

The broad participation in creating the requirements specification ensured the architecture of a comprehensive solution that would be complete in nature. Some primary requirements are:

Easy to adopt--to overcome cost, time and risk deployment issues.

Incremental to existing infrastructure--overlay on top of methods in place.

Non-intrusive to existing practices, methodologies and flows

Serves IP/re-use methodologies with a minimal incremental effort

Consolidated view of the power strategy for a design into a single entity

Comprehensive in capabilities to support the most advanced existing low power design techniques, across the entire continuum of design automation.

Extensible to new low power design techniques and to broader design flow scope (up to system-level and into analog mixed signal in particular).

A bottom-up analysis has led to support for a digital RTL to sign-off solution. Although limited in scope, the solution is broad in terms of design automation technology inclusion:

Adopting the Common Power Format into standard design flows will have fundamental benefits to those that use it along with industry leading tool solutions. It

Enables RTL functional verification to validate power related operation

Guarantees higher design quality with fewer functional failures

Reduces risk in applying state-of-the-art low power design techniques

Increases productivity and reduced cost of using those power saving methods

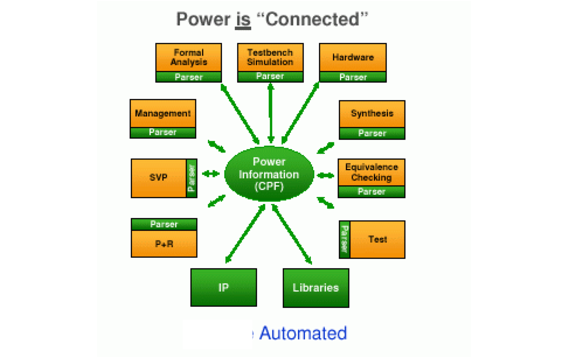

Figure1-2 shows the benefit of the Common Power Format in the design flow.