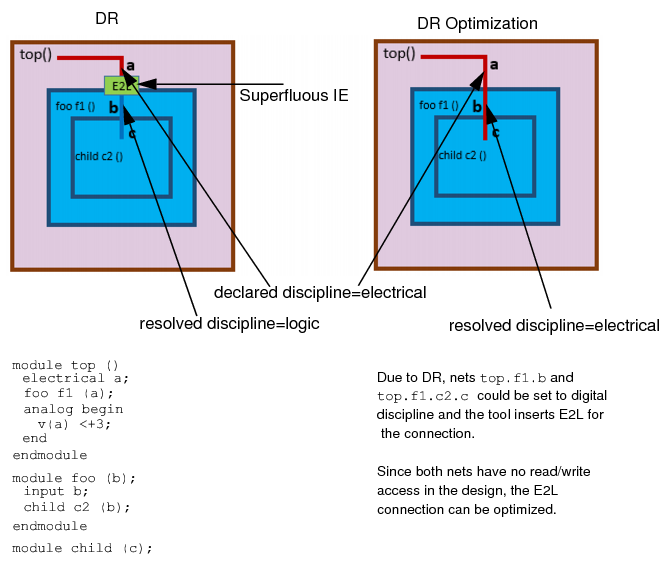

In Spectre AMS Designer, insertion of interface elements (IEs) is based on discipline resolution (DR). IEs are inserted along the analog/digital boundary, if a net is set, declared, or resolved to a digital discipline and connects to an analog node. Nets with declared discrete discipline express an explicit digital domain, whereas, nets with resolved or set discipline are interconnects that acquire their domain during elaboration.

Sometimes, interconnects are not used in digital context, however, they still acquire a discrete discipline, which causes superfluous IEs to be inserted along the analog/digital boundary. The simulator automatically handles such situations and optimizes these nets to an analog node. As a result, an interface element is not required for such connections.

Discipline resolution optimization can be enabled by using the xrun option -amsdropt.

Unlike in a connectmap card, the discipline parameter in an ie card can accept only a single discipline value.