Single-Level IE Optimization

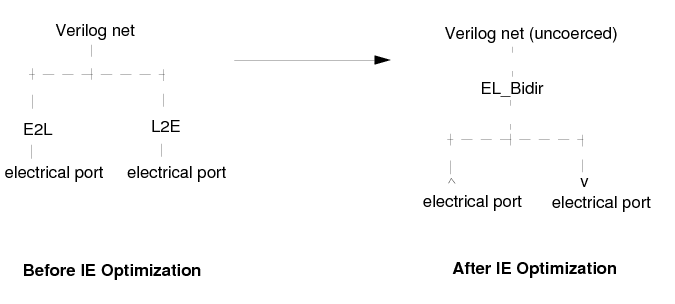

Single-level IE Optimization is a process in which the elaborator inserts a single bidirectional interface element (IE) in place of multiple IEs when the following conditions are met:

- A verilog net (logic, real, or user-defined type) forced to digital (using

$monitor,$display,force, OOMR reference in digital behavioral code, and so on) is connected to more than one analog port at thesame hierarchical level.

- Multiple dissimilar IEs exist between the digital net and the analog ports.

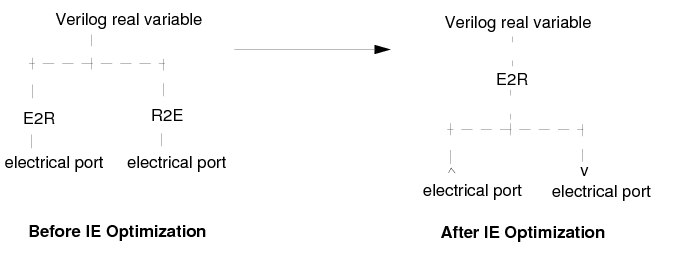

In case of analog/digital variable connections, multiple dissimilar IEs are replaced with a single electrical-to-real (E2R) IE that is connected to all the analog ports when:

- A real variable is connected to more than one analog port at the same hierarchical level.

- Multiple dissimilar IEs exist between the variable and the analog ports.

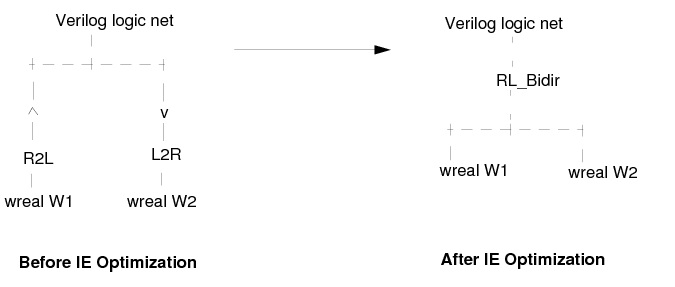

In case of nets involving real/logic connections, multiple dissimilar IEs between the logic net and the real or user-defined ports are replaced with a single real-to-logic (R2L) bidirectional IE when:

- A verilog net forced to digital (using

$monitor,$display,force, OOMR reference in digital behavioral code, and so on) is connected to more than one wreal or user-defined type port at the same hierarchical level.

- Multiple dissimilar IEs exist between the logic net and the real or user-defined ports.

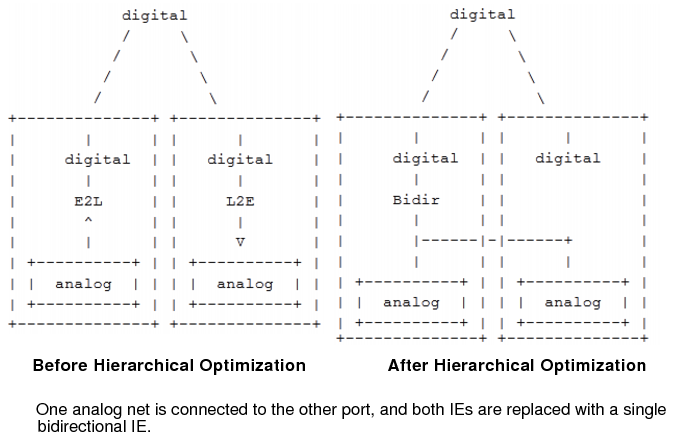

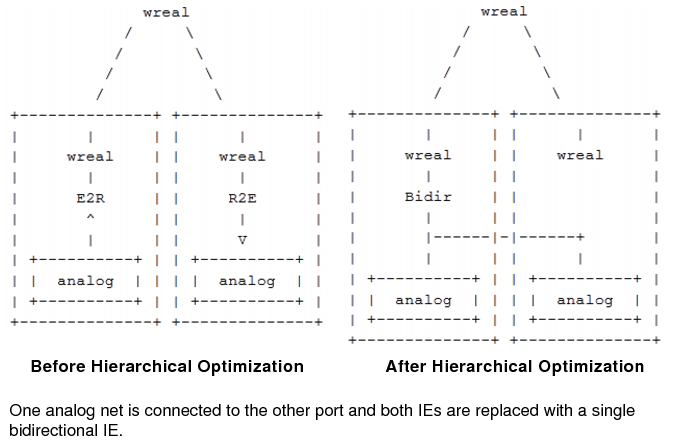

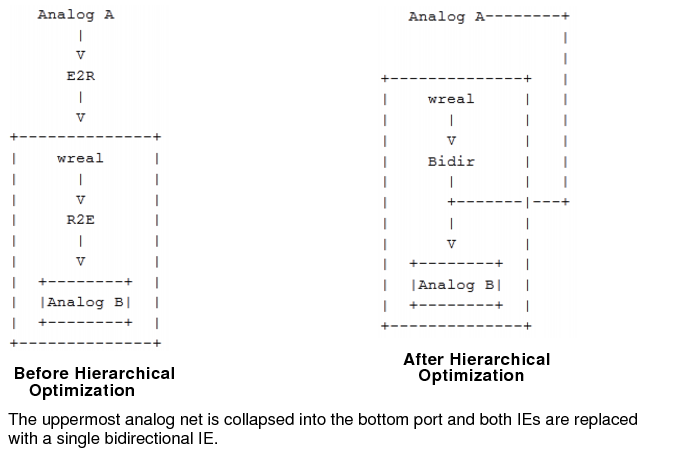

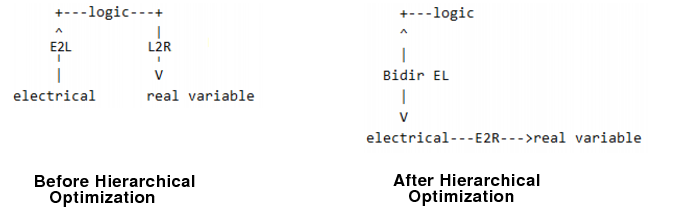

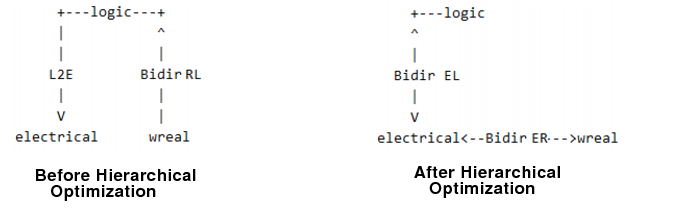

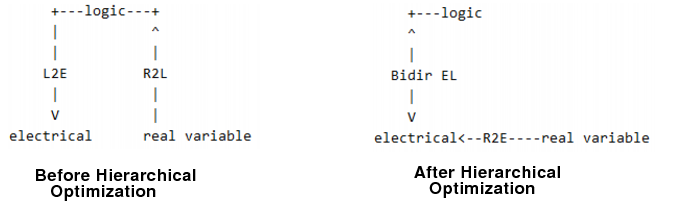

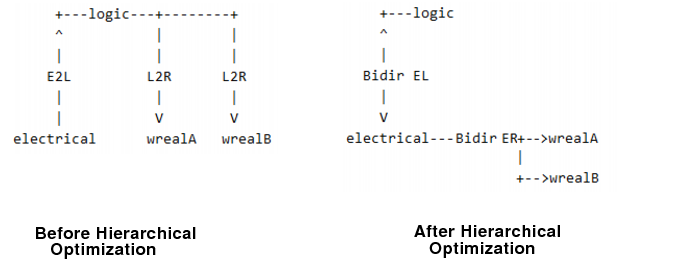

Hierarchical Optimization

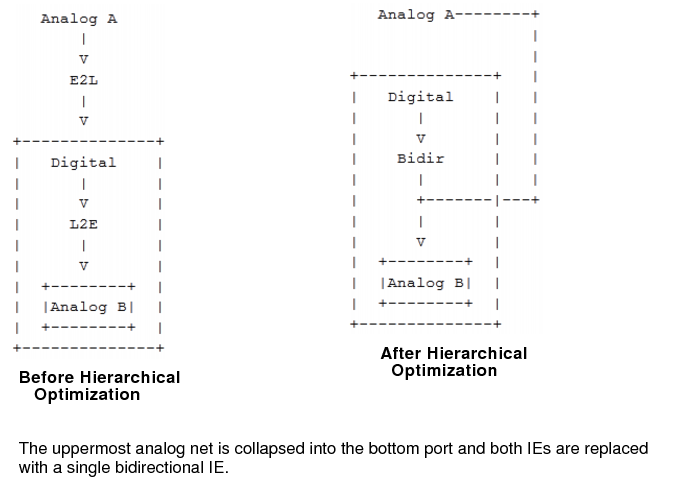

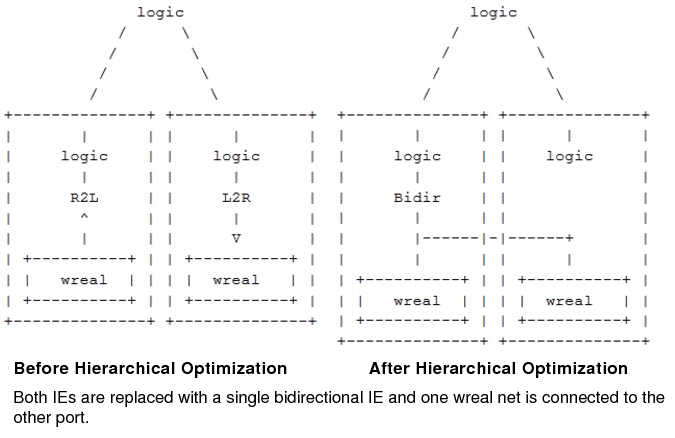

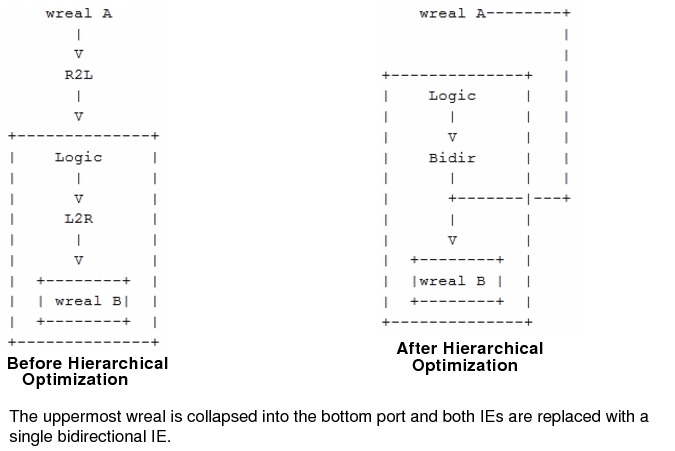

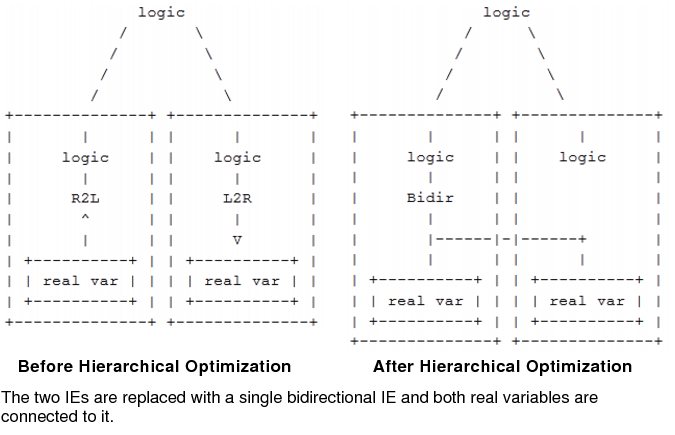

The interface elements (IEs) that are instantiated at any point on a hierarchical digital net can be combined into one. As a result, all IE-connected nets are collapsed while still maintaining the connection between the analog and digital nets. For this, the following criteria must be met:

- For discrete (logic or real) to electrical connections, there must be an electrical port to which all the IEs and electrical nets can be collapsed.

- For real net to logic connections, real nets are collapsed. However, logic nets are not collapsed.

- Multiple R2L or R2E IEs connected to a network of connected real variables and multiple connected real variables in different hierarchical scopes are not collapsed.

Examples

Digital Over Electrical Connections

Digital Sandwich

Logic over Wreal

Logic Sandwich

Logic over Real Variable

Wreal over Electrical

Wreal Electrical Sandwich

Interface Element Optimization between Dissimilar Nets

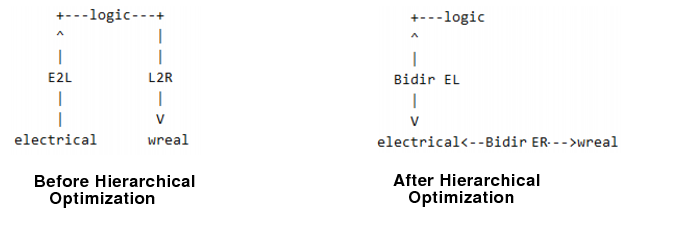

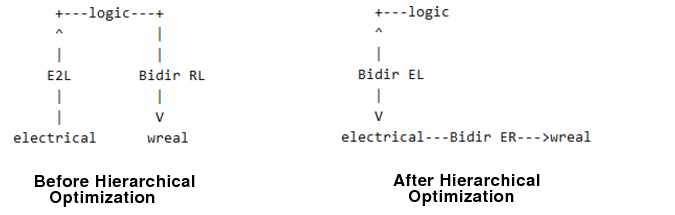

In Interface Element (IE) optimization between dissimilar nets, the elaborator inserts a bidirectional IE to collapse the electrical signal onto the real just like two electrical signals are collapsed in normal IE optimization. The structure of the resultant optimization depends on the following:

- The type of connect modules in the original configuration

- The type of objects (variables or nets) connected

Examples

Simple E-L-R connection

E-L-R with Bidirectional RL Connection

E-L-Real Variable

R-L-E with Bidirectional Connection

Real Variable-L-E Connection

Multiple Interface Elements

Multiple interface elements of the same type will be collapsed together during optimization, as shown below.

Hierarchical IE optimization is enabled by default. Hierarchical IE optimization is supported in the AMS-CPF flow. Currently, IE optimization is applied on nets only if the drivers/loads of the nets are associated with the same power domain.

According to the purpose of accuracy improvement, IE optimization does not occur for the following cases:

- Electrical net over logic ports

- Real variable over logic ports

- Real variable over electrical ports

You can use the -ieinfo xmelab/xrun option to generate a report that contains the connect module information used in the design.