Multi-Snapshot Incremental Elaboration (MSIE) is a technology that enables you to partition the design into sections based on the stability of the code. Parts of the design that are stable, or require only occasional changes, are placed into one or more primary partitions, while parts of the design that undergo frequent changes are placed into a separate incremental partition. Each partition is elaborated separately into a snapshot, and the snapshots are then combined at simulation time. When a change is made, only the affected partition is re-elaborated.

Incremental elaboration is also enabled for designs with mixed-signal behavior (either AMS or DMS).

Verilog-AMS is supported in primary partitions with the following restrictions:

- It is not allowed in the top-level modules of a primary partition if the module has ports.

- It is not allowed in modules containing instances that are left unbound using the

-incrbindoption. - SV-DC interconnect nets are not allowed in modules containing instances that are left unbound using the

-incrbindoption. - Wires in a top-level module of a primary partition do not coerce to

electricalorwrealif the module has ports. - Wires in modules containing instances that are left unbound using the

-incrbindoption does not coerce toelectricalorwreal.

Verilog-AMS is supported in incremental partitions with the following restrictions:

- It is not allowed in modules that bind to unbound instances in a primary partition.

- It is not allowed in modules containing instances that bind to primary partitions.

- SV-DC interconnect nets are not allowed in modules containing instances that bind to primary partitions.

- Wires in modules that bind to unbound instances in a primary partition do not coerce to

electricalorwreal. - Wires in modules containing instances that bind to primary partitions do not coerce to

electricalorwreal.

Use Models of Incremental Elaboration

Partitioning for UVM Test Modifications

Consider the following diagram where tb_top and dut are the primary partitions and tester is the incremental partition.

Here are how the restrictions apply for this example:

- Verilog-AMS is not allowed in

tb_topandtester - Wires in

tb_topdo not coerce toelectricalorwreal - Wires in

testerdo not coerce toelectricalorwreal - SV-DC interconnect nets are not allowed in

tb_top

Partitioning for a Stable DUT

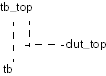

Consider the following diagram where dut_top is the primary partition and tb_top and tb are incremental partitions.

Here are how the restrictions apply for this example:

- Verilog-AMS is not allowed in

tb_topand in the top-level ofdut_top - Wire in the top-level of

dut_topdoes not coerce toelectricalorwreal - Wires in

tb_topdo not coerce toelectricalorwreal - SV-DC interconnect nets are not allowed in

tb_top

Flexible Partitioning for Complex SOCs

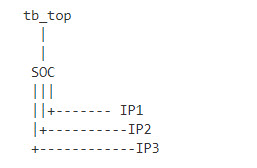

In the following diagram, tb_top and SOC are in one primary partition, while IP1, IP2, and IP3 are individual primary partitions.

The following restrictions apply for this example:

- Verilog-AMS is not allowed in top-levels of

IP1,IP2, orIP3 - Wires in top-levels of

IP1,IP2, orIP3do not coerce toelectricalorwreal - Verilog-AMS is not allowed in the modules in SOC that instantiate

IP1,IP2, andIP3 - Wires in the modules in SOC that instantiate

IP1,IP2, andIP3, do not coerce toelectricalorwreal - SV-DC interconnect nets is not allowed in the modules in SOC that instantiate

IP1,IP2, andIP3

Unsupported Scenarios of Incremental Elaboration for Mixed-Signal

The following are the unsupported scenarios:

- The

-autospiceoomrand-ignore_spice_oomrcommand-line options to manage Out-of-Module References (OOMR) to SPICE in digital statements - Low-power mixed-signal verification with multiple snapshots. See the limitations listed in the Incremental Elaboration in Low-Power Mixed-Signal Designs section.

- VHDL terminal port and VHDL-AMS on primary top

- Array of instances

- Discipline resolution at partition boundary port or net

-

Auto-MSIE functionality in designs containing Verilog-AMS or SPICE

- The

-spicetopoption to run a SPICE-on-Top design - AMS Virtuoso use model

Limitations of Incremental Elaboration for Mixed-Signal

Currently, the following limitations exist in incremental elaboration:

- Inherited connections must resolve to a net in the same partition as they exist either through defaults or through overrides. This prevents discipline resolution from propagating across the partition boundary; and, also eliminates the need for an interface element across the partition boundary. This requires that the global power supply nets in the

cds_globalsmodule is included as another top-level module in the primary partition. - Generating an

ieinforeport during primary elaboration is not supported. When anieinforeport is requested during the final elaboration, the list of interface elements also includes the ones from the primary partition. In addition, the hierarchical paths in the report are adjusted to the full path in the final design. - The

-amspartinfooption is currently not supported. - Multiple xrun flows are not supported for SPICE configurations.

- OOMR connection in incremental partition referring to an object of type

electrical,wrealin the primary partition or vice versa. - OOMR connection in primary partition referring to an object of type

analog,coerced wreal, orcoerced UDNin the incremental partition. - OOMR connection in primary partition referring to an object of type

wudnin the incremental partition. - OOMR connection to an analog node in the elaborated primary boundary.

- Analog OOMR connection to elaborated primary boundary or through internal

top_externsmodule. - Out of Primary References (OOPRs) from one primary partition to another.

- Connect modules at partition boundary.

- SystemVerilog interconnects at partition boundary.

- Discipline resolution of electrical nets at partition boundary.

- Verilog-AMS module with ports as a primary or incremental snapshot.

- SystemVerilog

wireconnect to VHDLrealport at partition boundary. - An incremental instantiate primary flow with an instance-based setting in the AMSD block, such as a config card or

iecard to do BDR setting, is not supported in primary elaboration. Instead, you must use the relative path of the primary top. - Programmable RNM coercion.

- Bind statement in incremental partition and bind target in a primary partition.

- SV bind statements on SPICE blocks (with

-xmcbind) on a spice internal node. - AMS and DMS nets cannot be declared or resolved across partition boundaries.

- SV wire connects to VHDL real port at the partition boundary.

- SPICE configurations in primary partition under multiple run mode.

- Back to Back interface elements (IE) at partition boundary.

- Binding of Verilog AMS module to primary or incremental snapshot target modules.

- RNM (wreal) coercion on specific scope (

-rnm_coerce on scopeType-scope) is not supported in the single xrun flow.