When reusing mixed-language testbenches, you can specify how you want the software to manage out-of-module references in digital statements when you substitute a SPICE block for a purely digital (Verilog) block. You can either use compiler directives around portions of your Verilog source code, or use a command-line option to specify your preference globally (without having to edit your Verilog source code). See the following topics for details:

- Using Command-Line Options to Manage Out-of-Module References to SPICE

- Using Compiler Directives to Manage Out-of-Module References to SPICE

Using Command-Line Options to Manage Out-of-Module References to SPICE

You can use the -autospiceoomr and -autospiceignore command-line options to specify how you want the software to manage out-of-module references (OOMRs) in digital statements when you substitute a SPICE block with a purely digital (Verilog) block.

When you use the -autospiceoomr option, the software automatically converts the SPICE OOMRs to appropriate digital values and vice versa. And, the software automatically prefixes X to spice instance names in OOMRs to spice ports or internal nets.

The software does a mapping of a digital OOMR having Verilog hierarchy instance names to an equivalent SPICE ports/nets. The software adds the prefix 'X' to spice instance names, if the instance names are specified without the prefix "X" in the verilog testbench.

However, if the spice instance name begins with "x" and also has the prefix "X", the software picks the instance name only. For instance, Xxa2 in the example: top.a1.Xxa2.a3.d: top.a1.xa2.Xa3.d.

For mixed circuit netlist, software adds prefix "X" to spectre instance name only if the instance name begins with "x" and the equivalent instance name is specified without the "x" in the Verilog testbench.

Consider the following example of a Verilog testbench where SPICE subckit, ana1 and Spectre subckit, mycell are instantiated:

module top(); ana1 a1 (out1); mycell m1 (a, b); dig_monitor D1 ();endmodule

module dig_monitor(); initial begin // we want to plot the d bus values after E2L conversion #10 $display( "======= %M internal bus0= %h", top.a1.Xxa2.a3.d,, top.m1.i1.i22.pa,,top.m1.i1.i22.pb); endendmodule

The following example illustrates the spice netlist and spectre netlist where the sub-circuits anal and mycell are defined:

anal.sp:

.subckt ana3 out1I0 0 d 1.5uR0 d 0 1meg.ends.subckt ana1 out1Xxa2 out1 ana2.ends.subckt ana2 out1a3 out1 ana3.ends.tran 1n 100u.probe V(*).end

mycell.scs:

subckt mycell pa pbi1 (pa pb) mycell2ends

subckt mycell2 pa pbi22 (pa pb) mycell3ends

subckt mycell3 pa pbi31 (pa 0) vsource dc=2i32 (pb\[0\] 0) vsource dc=2i33 (pb\[1\] 0) vsource dc=2ends

And, in the AMSD control file, a1 and m1 are replaced by sub-circuits, ana1 and mycell, respectively as follows:

include "mycell.scs"

amsd{ ie vsup=1.8 portmap subckt=ana1 config cell=ana1 use=spice portmap subckt=mycell config cell=mycell use=spice}

Note that in the above Verilog testbench the spice instance xa2 is specified with a prefix "X" and the xa3 is specified without the prefix "X". When you use the -autospiceoomr command-line option, the software automatically does the following mapping for the spice instance names:

top.a1.Xxa2.a3.d: top.a1.xa2.Xa3.d:top.m1.i1. i22.pa: top.m1.i1. i22.pa:top.m1. i1. i22.pb: top.m1.i1. i22.pb:

When you use the -autospiceignore command-line option, the software ignores any digital statements that contain OOMRs to SPICE blocks. You can specify one of the following logic values to the –autospiceignore option: x|z|0|1.

In the following example, if you specify -autospiceignore x, assertion that is triggered at time 0 as d1.x is forced to x. And, if you specify the value as -autospiceignore 1, assertion that is not triggered as ‘1.x is forced to 1.

module tb;wire w;…//SPICE blockdut d1(w);…assign w = 1’b1;always @(w) beginassert (d1.x != 1’b0) else begint = $time;$error(“assert failed at time %0t”, t);endend…endmodulemodule dut(x);input x;…endmodule

If both –autospiceoomr and –autospiceignore options are specified, -autospiceignore option gets the higher priority.

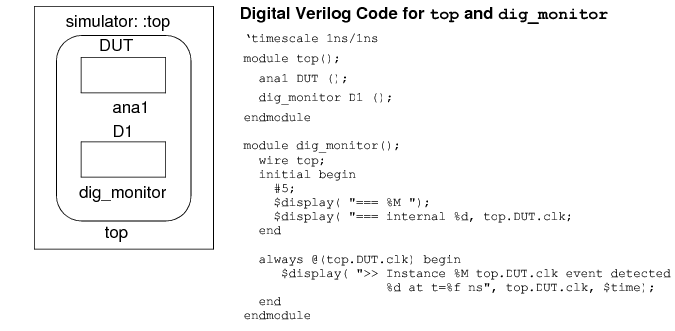

Consider the following example:

DUT is replaced by a SPICE subcircuit in the AMS control file, as follows:

//amscf1.scs fileinclude "source/spice/ana1.sp"amsd{ ie vsup=1.8portmap subckt ana1config cell=ana1 use=spice}

When the simulation is run using the xrun command

xrun -clean -mess source/verilog/top1.v -timescale 1ns/100ps -iereport amscf1.scs

the simulator generates an error related to OOMT top.dut.clk.

When you use the -autospiceignore command-line option with xrun, the simulator ignores the SPICE OOMR references and the simulation runs successfully.

When you use the -autospiceoomr command-line option with xrun, the simulator automatically converts the SPICE OOMR to a digital value. For example, the IE report will display the following:

Automatically inserted instance: cds_autospiceoomr.top_DUT_clk__E2L_2__electrical (merged):

connectmodule name: E2L_2, inserted across signal: top_DUT_clk and ports of discipline: electrical Sensitivity infomation: No Sensitivity info Discipline of Port (Ain): electrical, Analog port Discipline of Port (Dout): logic, Digital port Drivers of port Dout: No drivers Loads of port Dout: No loadsIE Report Summary: E2L_2 ( electrical input; logic inout; ) total: 1 -------------------------------------------------------------------Total Number of Connect Modules total: 1

You can also use the -ignore_spice_oomr and -default_spice_oomr command-line options to manage out-of-module references in digital statements when you substitute a SPICE block for a purely digital (Verilog) block. These options affect the following digital statements:

ifstatements$displayor$monitorstatements- Procedural assignments, including blocking and nonblocking

forceandreleaseprocedural statements- Continuous assignments

- Sequential blocks (where the out-of-module reference to SPICE is in a delay or event control expression)

The -ignore_spice_oomr and -default_spice_oomr command-line options will be removed in a future release.

See also "Using Compiler Directives to Manage Out-of-Module References to SPICE."

Using Compiler Directives to Manage Out-of-Module References to SPICE

You can use the `ams_testbench_reuse_ignore and `ams_testbench_reuse_default_value directives to specify how you want the software to manage out-of-module references in digital statements when you substitute a SPICE block for a purely digital (Verilog) block. You can use these directives in conjunction with the following statements:

ifstatements$displayor$monitorstatements- Procedural assignments, including blocking and nonblocking

forceandreleaseprocedural statements- Continuous assignments

- Sequential blocks (where the out-of-module reference to SPICE is in a delay or event control expression)

When you use the `ams_testbench_reuse_ignore directive, the software ignores any digital statements that contain out-of-module references to SPICE blocks. For example:

`ams_testbench_reuse_ignore

if ( spice_oomr_ref )

$display("1");

else

$display("2");

$display("3");

`end_ams_testbench_reuse_ignore

In this example (above), the software ignores $display("1") and $display("2") , but $display("3") remains active.

When you use the `ams_testbench_reuse_default_value directive, the software assigns a default value (1'bx) if it encounters a digital statement that contains an out-of-module reference to a SPICE block.

For example, if you substitute a SPICE block such that testbench.p1.p0 becomes an out-of-module reference in the following testbench code, the `ams_testbench_reuse_default_value directive causes the software to set the value in the statement to 1'bx.

module testbench ();

...

wire vcoclk, clock_2, clock_1, clock_0, net036, p0;

...

`ams_testbench_reuse_default_value

initial begin

$monitor (testbench.p1.p0);

end `end_ams_testbench_reuse_default_value

...

pll_top p1(refclk, reset, vcoclk, clock_2, clock_1, clock_0, net036, p0,

clk_p0_1x, clk_p0_4x);

endmodule

See also "Using Command-Line Options to Manage Out-of-Module References to SPICE."

Using Bus Delimiters with Out-of-Module References to SPICE

You can use the -autospice_addbusdelim option to specify additional bus delimiters apart from the default ones, "[] <>" to enable spice out-of-module references (OOMRs). It allows you to use the bus delimiters in all SPICE buses/ports including the ones in ports at HDL boundary as well as internal ones.

The -autospice_addbusdelim option works only for auto SPICE OOMRs; therefore, you must specify the the -autospice_addbusdelim option along with the option as follows:

xrun -autospiceoomr -autospice_addbusdelim "_ __ && empty ( % %%"

The single delimiter _ is used between bus base-name and index; the pair delimiters, __, &&, and %% are used around the index; and, empty is used for NULL delimiter- for example "abc0, abc1".

The following example illustrates that _ works for vector i in subckt, spice_middle; __ works for i0; && works for i1; empty works for abc; ( works for i2; % works for i3; %% works for i4:

// amscf.scs

amsd{ ie vsup=1.8 portmap subckt=spice_middle file="./spice_middle.pb" config cell=spice_middle use=spice}

// top.vmodule top; wire [0:3] i; wire [0:3] o; spice_middle x0 ( i, o ); initial #3 $display("==== ", top.x0.i,,top.x0.out,,top.x0.i0,,top.x0.i1,,top.x0.i2,,top.x0.abc,,top.x0.i3,,top.x0.i4);endmodule

// spice.scs

subckt spice_middle ( i_3 i_2 i_1 i_0 out\<3\> out\<2\> out\<1\> out\<0\>)v19 ( i4\%3\% 0) vsource dc=5v18 ( i4\%2\% 0) vsource dc=5

v17 ( i3\%3 0) vsource dc=5v16 ( i3\%2 0) vsource dc=5

v15 ( abc1 0) vsource dc=5v14 ( abc0 0) vsource dc=5

v13 ( i2\(2 0) vsource dc=5v12 ( i2\(1 0) vsource dc=5

v11 ( i1\&1\& 0) vsource dc=5v10 ( i1\&0\& 0) vsource dc=5

v9 ( i0_3_ 0) vsource dc=5v8 ( i0_2_ 0) vsource dc=5

v7 ( i_3 0) vsource dc=5v6 ( i_2 0) vsource dc=5v5 ( i_1 0) vsource dc=5v4 ( i_0 0) vsource dc=5

v3 (out\<3\> 0) vsource dc=5v2 (out\<2\> 0) vsource dc=5v1 (out\<1\> 0) vsource dc=5v0 (out\<0\> 0) vsource dc=5ends