A typical SoC Verification flow involves top-level simulation of components at various levels of abstraction. The verification engineer needs to integrate modules from the analog and digital design team as well as from third-party IP providers. Each module in itself could be a mixed-signal design that is created using either an analog-centric or a digital-centric use model.

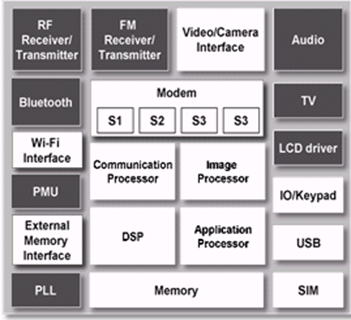

The design descriptions could be schematics, SystemVerilog, and Verilog (or VHDL)-AMS in a single top-level SoC verification. The following figure illustrates this scenario (the dark gray blocks are analog or mixed-signal blocks).

At present, functional complexity in terms of modes of operation, extensive digital calibration, and architectural algorithms overwhelms the traditional verification methodologies.

Simulation at this top level is extremely costly (both in terms of time and licensing cost) because a significant amount of the SoC has to be simulated inside the analog engine. Finding a way to reduce the time and expense to verify the SoC, while trading off some accuracy that is not needed at this high level of integration, is extremely important. In fact, the basic models of the analog parts might be sufficient for the verification steps.

The verification problem is hierarchical, as the design is created in a hierarchical fashion. The top-level SoC is the highest level of integration and can be tested using the top-level verification step. Verification steps are much cheaper and easier on smaller blocks because the simulation performance is better and the verification tasks are more limited. Nevertheless, the integration of multiple blocks needs to be verified to ensure that the interfaces work correctly and the blocks work together smoothly.

Generally, the verification goal is split into two parts: fulfilling the specification requirements and verifying that the system works correctly.

The verification tasks require a certain amount of simulation data, data accuracy, and the right simulation context. For example, a detailed analysis of an RF low noise amplifier requires very high simulation accuracy, whereas checking the pin connectivity for the same block has an extremely low sensitivity towards accuracy. On the other hand, the pin connection check requires the block to be simulated in the context of the surrounding circuitry whereas the RF checks might be relatively independent of the integration.

Consequently, a full-chip simulation using the highest level of simulation accuracy would be desirable to fulfill all verification requirements at the same time. However, the limiting factor in this context is simulation performance. Even though the simulation performance of current simulation tools has greatly improved (by using the fast SPICE methods), the increased complexity of designs continues to limit detailed verification by time and simulation performance. On the other hand, very few verification goals require a high level of simulation accuracy within a full-chip simulation context.

The practical way around this problem is a hierarchical verification approach that uses different levels of design abstractions for different verification goals. For the analog circuit part, common levels of abstraction are:

- Extracted transistor netlist including parasitic elements

- Transistor-level SPICE simulation

- Transistor-level fast SPICE simulation

- Analog/conservative behavioral modeling

- Real value modeling

- Pure digital model

The gain in simulation performance and the reduction in accuracy are highly dependent on the application. The target application of real number modeling (RNM) is to bridge the gap between the performance requirements for a full chip simulation and the accuracy limitations of a mixed-signal design. A significant speed-up in simulation performance and reduction in the license cost can be achieved by replacing the analog portions of the SoC with functionally equivalent real number models that do not require the analog engine.