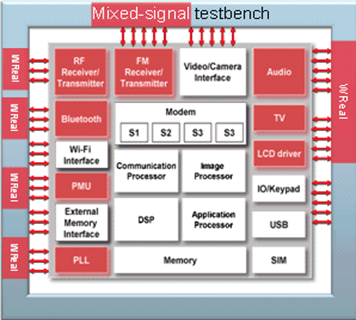

Real Number Modeling (RNM) is a method by which you can perform verification of analog or mixed-signal designs using discretely simulated real values. This allows simulation using only the digital solver, avoiding the slower analog simulation and enabling intensive verification of mixed-signal design within a short period. The Mixed-Signal SoC with wreal Models and Testbench figure illustrates how the analog portions of the design are replaced with functionally equivalent real number models (shown in red).

Most of the system verification in analog, digital, and the mixed-signal domain is based on simulation runs. To meet the verification goals, a certain amount of simulation data and data accuracy are required. For example, a detailed analysis of an RF low noise amplifier requires very high simulation accuracy, but a single RF sinusoid period might be sufficient. On the other hand, a pin connectivity check for a large digital block has an extremely low sensitivity towards accuracy but may require a long transient simulation time to cover all sorts of events and states.

RNM is an interesting add-on to classical mixed-signal verification approaches, such as SystemVerilog, Verilog, and SPICE mixed-signal simulation or pure digital modeling of the analog block in the mixed-signal design. It is not meant to replace other verification tasks including detailed analog performance verification. These tasks are still needed to ensure the correct behavior of the block. RVM complements the methodology with a high simulation performance configuration mainly targeting the functional verification goals. In addition, typical analog simulation problems, such as convergence issues, very small-time steps, and capacity and performance limitations are eliminated while maintaining the fundamental analog, meaning continuous value, and behavior of the circuitry.

There are four different language standards that support RNM such as:

- wreal ports in Verilog-AMS

- wreal nettypes in SystemVerilog

- wreal in VHDL

- wreal types in e

Real valued models are obviously limited due to the signal flow approach. On the other hand, this modeling limitation is an enabling factor that is able to solve the equations inside the digital kernel. Simple analog primitives, like a resistor, are impossible to model as a real number model. The branch current through the terminals and the voltage across both pins are defined as a fixed ratio, however, there is no signal flow representation for this.

The same limitation applies to an analog RC filter. However, in most cases it is relatively straightforward to convert the analog filter characteristic, using the bilinear transform, into a discrete domain filter. A z-domain filter is easy to implement in real values.

This means a real number model is always an abstraction above and beyond the analog behavioral details. Given the target application described above for functional verification of the analog and digital integration check, this would be a mandatory step anyway.

Detailed analog behavior, such as impedance matching, transistor sizing, continuous-time feedback, low-level RC coupling effects, sensible nonlinear input/output impedance interactions, noise level, and similar effects need to be verified on the lower analog block level using conservative behavioral models or transistor-level representations.

Model Verification

Top-level verification based on real number models is only as good as the models themselves. Thus, a model verification step is mandatory for bottom-up models. In most cases, the transistor-level implementation is used as a reference implementation for the real-number models. Simulation setup and test benches are available in the analog block-level flow for these blocks.

To verify the model versus the reference, identical simulations are performed using the reference, and the model and the simulation results are compared. This can be done manually or using Wave Compare in Maestro (Assembler), to set up the simulation runs and result comparison.