The AMS Designer simulator and Xcelium simulator with mixed-signal option let you use SystemVerilog Assertions on SystemVerilog real variables (or ports) that connect to or electrical nets, and PSL assertions on real and Verilog-AMS wreal nets that connect to electrical nets.

PSL stands for the property specification language that is undergoing standardization as IEEE 1850 Property Specification Language.

SystemVerilog Assertions

In mixed-signal designs, you can specify a SystemVerilog Assertion (SVA) on a SystemVerilog real port that connects to a wreal or electrical net. You can use the SVA to check the value of the wreal or electrical net.

When you connect a SystemVerilog real port to an electrical net, the elaborator inserts the appropriate real-to-electrical or electrical-to-real interface element automatically.

In the following example, SystemVerilog real number ports (r, xr, and wr) are connected to nets belonging to the electrical domain and nets of type wreal.

module top;

var real r, xr, wr;

assign xr = 3.14;

ams_electrical_src e_s1(r); // causes insertion of Electrical2Real connection

// module

ams_electrical_dst e_d1(xr); // causes insertion of Real2Electrical connection

// module

ams_wreal_src w_s1(wr); // Connects SystemVerilog real variable to wreal

endmodule

module ams_electrical_dst(e);

input e; electrical e; initial #10 $display("%M: %f", V(e));

endmodule

module ams_electrical_src(e);

output e; electrical e; analog V(e) <+ 5.0;

endmodule

module ams_wreal_src(w);

output w; wreal w; assign w = 2.5;

endmodule

Once the SystemVerilog real variables import the AMS functionality through the code above, they can appear in any SystemVerilog assertion statement that permits the use of real variables. real variables can be used in SystemVerilog assertion, real variable, r, that comes in as a wreal port (from the ams_design instance), w:

module sv_tb;

real r;

time t;

ams_design a1(r);

always @(r) begin

assert (r < 5.5) else begin

t = $time;

$error("assert failed at time %0t",t);

end

end

endmodule

module ams_design(w);

output w; wreal w;

assign w =5.6;

end

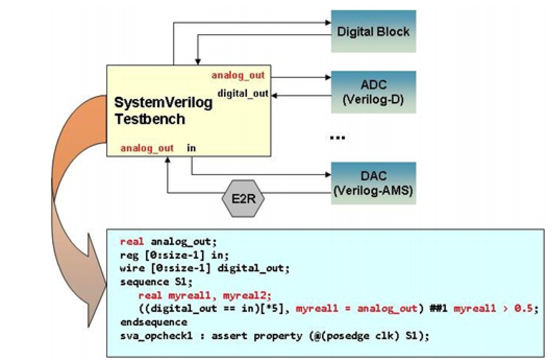

The SystemVerilog real variable used inside a SystemVerilog assertion figure shows another example of a SystemVerilog real variable being used inside a SystemVerilog assertion.

Analog System Tasks in SVA

SystemVerilog Assertions (SVA) can contain analog system tasks like $cds_get_analog_value() to access the values of analog objects for use within assertions. SVA semantics specify the use of sampled values of all signals, except local variables, during assertion evaluation.

However, if any digital signal changes during assertion evaluation, there is the risk of sampling analog objects (via $cds_get_analog_value()) too. This is not acceptable because values of such analog objects could have changed significantly since the last sampling and may be out of date for a fair evaluation.

Consider the following example:

default clocking CLK @(negedge clk); endclocking

assert property ( a & !b |-> $cds_get_analog_value("top.simpleVAMS.x") > c);

The signals of the assertion above would be sampled whenever digital signals, 'a', 'b', 'c', or 'clk' change, whereas the assertion would be evaluated at the negative edge of 'clk'.

So the value of the expression $cds_get_analog_value("top.simpleVAMS.x") > c used in the assertion evaluation would be the value that existed when the signals were sampled the last time.

To eliminate the evaluation error caused by this, the assertion evaluation process treats the expression just like local variables and uses the current value of the expression

$cds_get_analog_value("top.simpleVAMS.x") > c

Note, however, that like local variables, it uses the current value of ALL digital signals in the expression that contains the analog system function. In this case, the current value of ' c ' would be used.

This can cause race conditions when such digital signals change on the same edge as the clock. This is currently a limitation in the general assertion solution.